點此購買

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

HoneRiSO Rip

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

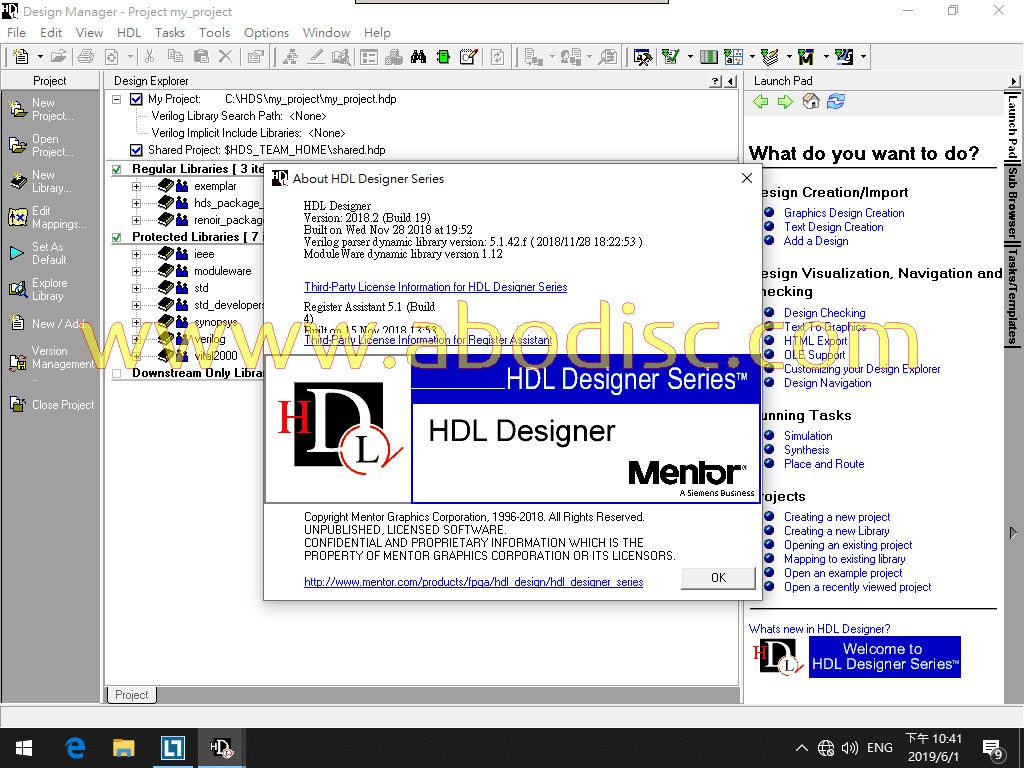

軟體名稱: Mentor Graphics HDL Designer Series 2018.2

語系版本: 英文版

光碟片數: 單片裝(單面 DVD)

保護種類: 授權檔

破解說明: 見最底下

系統支援: 適用 64 位元的 Windows 7/8/8.1/10

硬體需求: PC

軟體類型: 硬體描述語言

更新日期: 2019.01.27

軟體發行: Mentor Graphics(O.D)

官方網站: http://www.saros.co.uk/products/eda/tools/hdl-designer-series

中文網站: 無

軟體簡介: (以官方網站為準)

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

Mentor Graphics HDL Designer 設計製作和流程管理系列工具 HDL Designer為提

高設計效率和設計品質提供了無與倫比的靈活手段和功能。通過圖形化、文字或兩

者的組合,結合 IP 的引入,快速高效的製作設計,HDL 可視化和統一的HDL 風格

和檔案能力,版本管理為團隊設計提供了基礎,全面的 mixed-HDL、Verilog VHDL

、支援適應百萬門的 FPGA,ASIC 和 SoC 設計。與模擬工具如 ModelSim和綜合工

具如 Precision 結合提供完整的 FPGA/ASIC 設計流程

明導國際 (Mentor Graphics) 最近為 HDL Designer Series 設計環境新增了多套

RTL 編碼規則庫,可支援 Altera 和 Xilinx 等業界主要 FPGA 廠商的可程式邏輯

元件; 另外,Mentor 也宣佈其最新的 HDL Designer 工具將會整合強大的並行設

計檢查功能。

HDL Designer Series 能在設計輸入過程的同時執行先進設計檢查,這套工具可透

過快速精確的分析和錯誤辨識來減少錯誤機率,其適用範圍不僅涵蓋普通HDL 程式

碼,還包括特定廠商的 FPGA 規則。

Mentor 聲稱,HDL Designer 的先進靜態檢查技術能讓工程師在設計流程初期找出

潛在的 HDL 設計問題,進而幫助廠商儘早解決潛在的設計錯誤。 對 FPGA 廠商規

則的支援還能確保往後採用 Altera 或 Xilinx 元件的設計從一開始就能重複使用

HDL 程式碼。

「除了找出所有可能的一般性 HDL 設計問題外,設計人員還能以最適合其架構並

被推薦採用的 Altera 和 Xilinx 廠商元件規則集做為參考標準,再利用新版 HDL

Designer Series 工具檢查其 HDL 程式碼的精確度,」 Mentor Graphics 設計輸

入事業單位總經理 Glenn Perry 表示。

介紹

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

站長安裝測試環境與安裝說明:

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

‧測試環境 Windows 10.1903 64位元繁體中文企業版、AMD CPU、4 GB 記憶體。

‧見光碟 "安裝說明.txt" 中文說明

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=

-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-= |